JANUARY 2026

HiPEAC 2026

Kraków

**Digital sovereignty: what, why, and how?**

**How Michaela Blott tailors custom compute for efficient AI**

**Frank Karlitschek on providing an alternative to US cloud platforms**

**Navigating the impact of AI on hardware, with Deming Chen**

# Contents

## Michaela Blott on the efficiency of tailored compute

## Frank Karlitschek on alternative collaboration platforms

## How AI is transforming hardware, with Deming Chen

3 **Welcome**

*Koen De Bosschere*

4 **HiPEAC voices**

**'Pairing novel algorithms with custom hardware architectures could enable step-change improvements in model capability, energy efficiency and performance'**

*Michaela Blott*

6 **HiPEAC voices**

**'With Nextcloud, we have now an alternative to the big collaboration platforms from the United States'**

*Frank Karlitschek*

8 **HiPEAC voices**

**'While AI-assisted hardware design is far from a solved problem, it is well positioned to fundamentally reshape how hardware systems are conceived, built, verified, and deployed'**

*Deming Chen*

11 **HiPEAC news**

14 **Ecosystem evolution**

**Swarmtelect, Anyway Systems, Exein, NobodyWho, Cloudberry, Wodan AI, MachineWare, Sainet**

16 **Community news**

19 **Digital sovereignty special**

**'By not controlling our critical digital infrastructure, we have ceded control over our economic future and our ability to uphold our own laws and values'**

*Cristina Caffarra and Stéfane Fermigier*

27 **Digital sovereignty special**

**Encoding cloud sovereignty: How Europe is getting serious about homegrown cloud**

*Stanisław Krzyżanowski*

28 **Digital sovereignty special**

**'Digital sovereignty has profound implications for the way in which our democracies operate'**

*Alberto P. Martí*

30 **Digital sovereignty special**

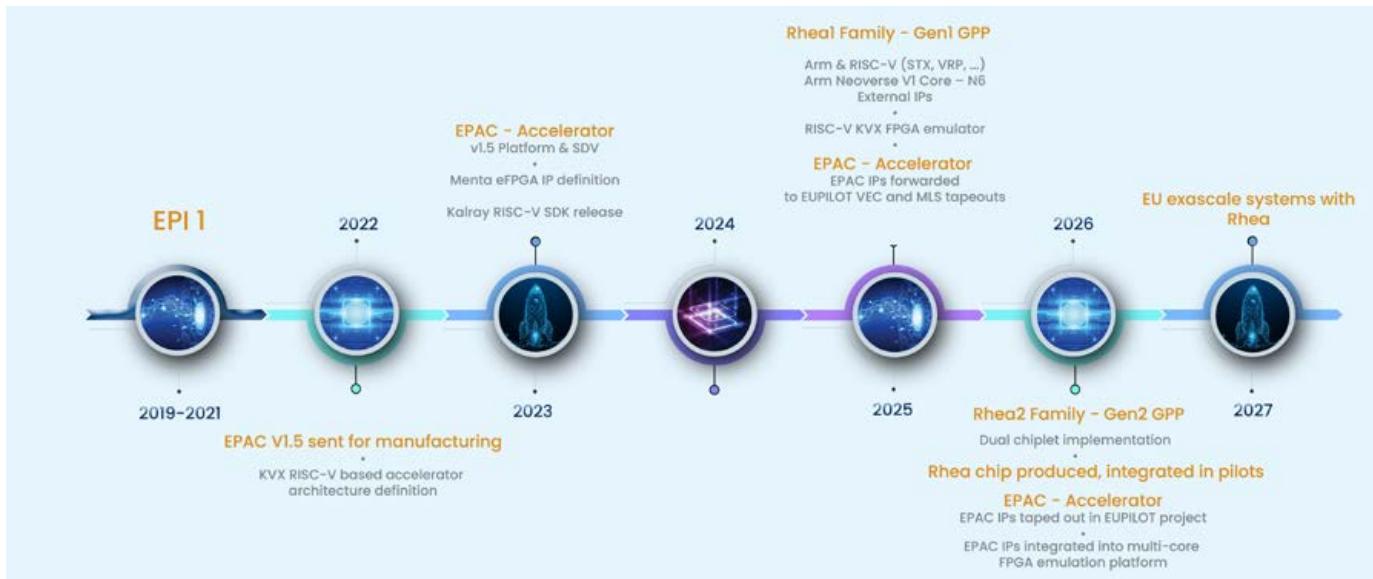

**Advancing Europe's digital sovereignty: The role of EPI, EUPEX, EUPILOT, and DARE**

*Katarina Vukušić and Romana Konjevod*

32 **Digital sovereignty special**

**Introducing the European Unified RISC-V IP Access Platform (UAP)**

*Florian Wohlrab*

34 **Trustworthy computing systems**

**TrustWeave: Weaving verifiable trust into Europe's digital infrastructures**

*Alessandro Cilardo*

36 **Trustworthy computing systems**

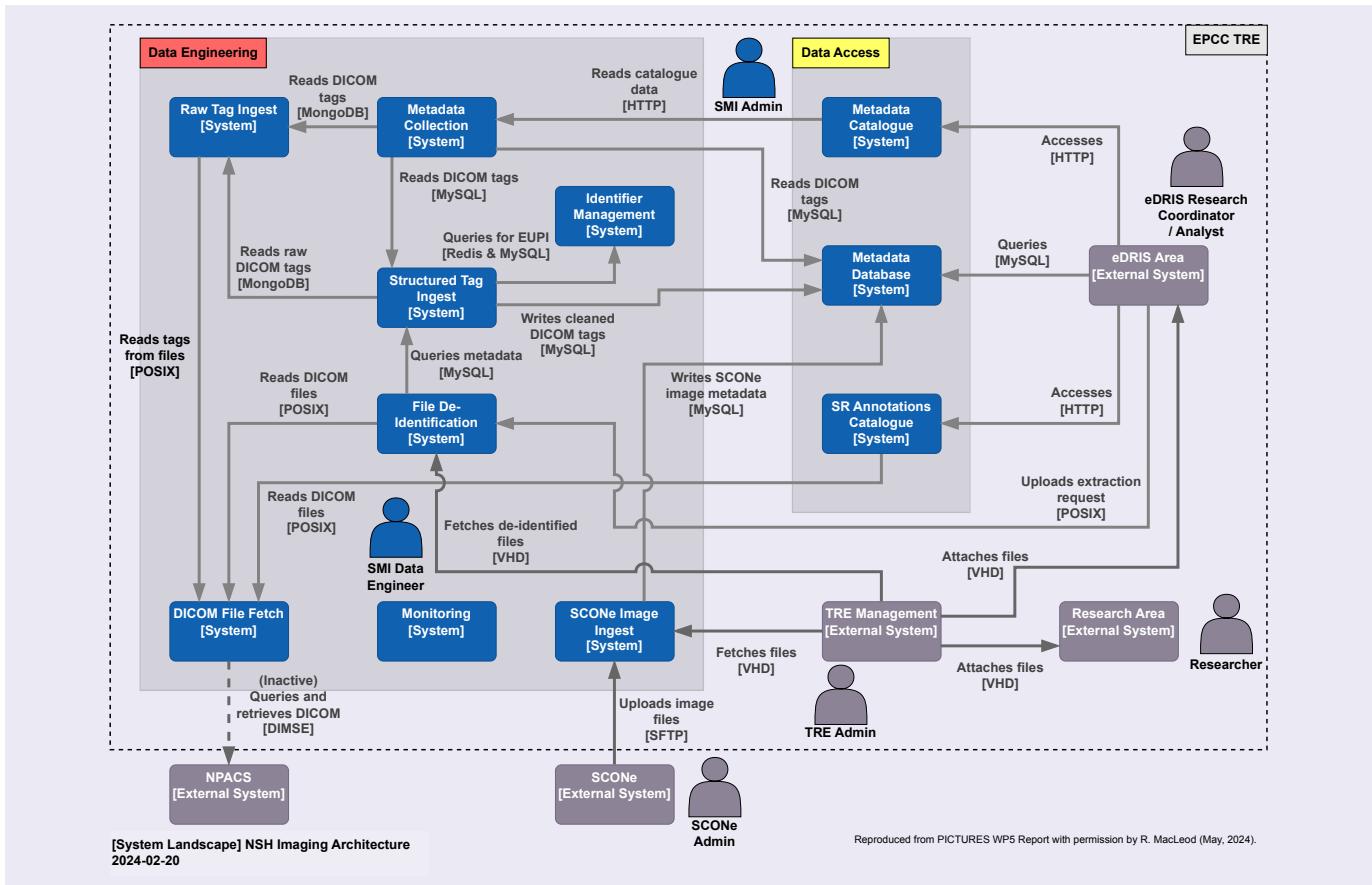

**Towards a harmonized definition of data safe havens**

*Jano van Hemert*

38 **Trustworthy computing systems**

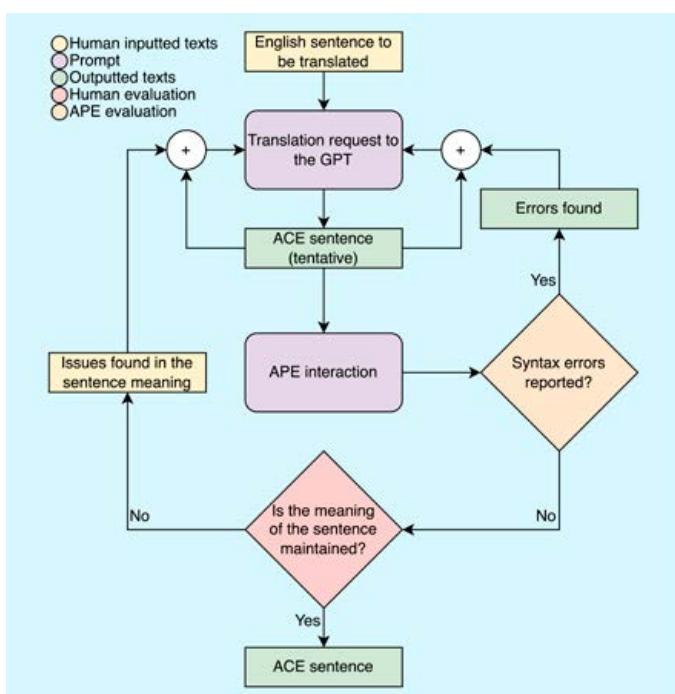

**Building trustworthy legal intelligence: From explainable AI to controlled natural language**

*Grazia Garzo and Alessandro Palumbo*

40 **Innovation Europe**

**Fortifying the foundation: RESCALE's revolution in secure supply chains**

*RESCALE project consortium*

42 **Innovation impact**

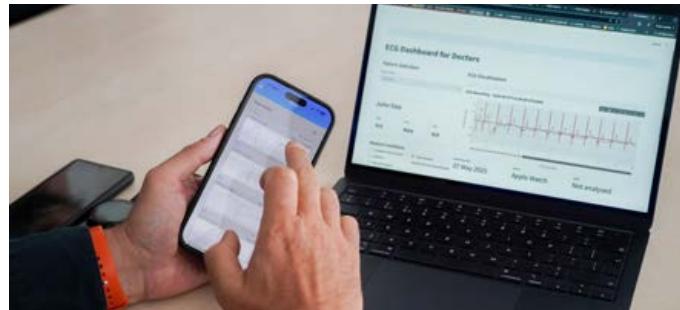

**From research to market: How a European AI breakthrough became a scalable solution for stroke prevention**

*Ariadna Rodriguez, Davide Cirillo and Daniele Lezzi*

44 **Peac performance**

**EPSILOD: Open-source framework for iterative stencil loops on highly heterogeneous distributed systems**

*Manuel de Castro and Arturo Gonzalez-Escribano*

46 **HiPEAC futures**

**Boosting careers at the HiPEAC STEM Student Day**

**Three-minute thesis: Architectures and frameworks for near-memory computing using 3D-stacked memories**

Photo credit: vectorfusionart | stock.adobe.com

# HiPEAC Technology Transfer Awards 2025

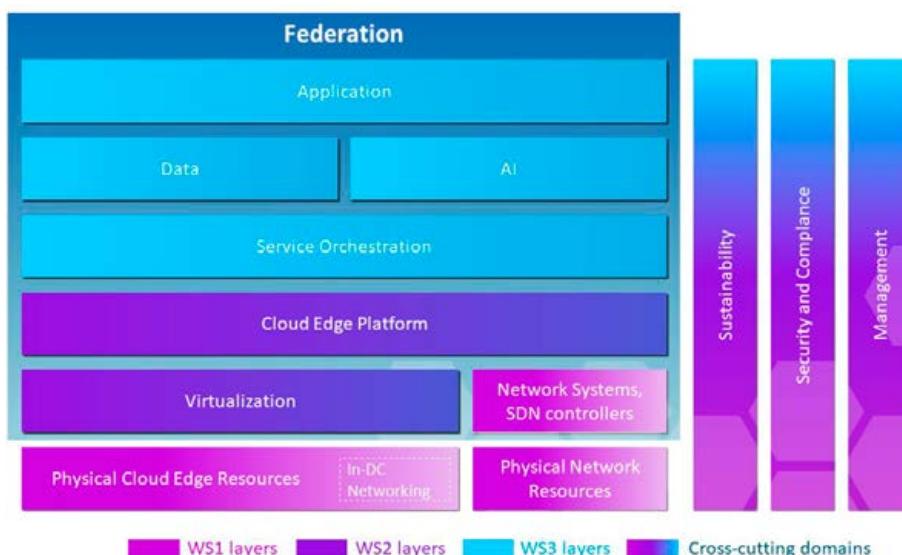

## Building digital sovereignty and capacity in Europe

## EU technology initiatives for a sovereign Europe

Spanning the compute continuum from edge to cloud, HiPEAC (High Performance, Edge And Cloud computing) is a network of over 2,000 world-class computing systems researchers, industry representatives and students. First established in 2004, the project is now in its seventh edition. HiPEAC7 focuses on networking and roadmapping activities: bringing the computing community together in Europe, exchanging ideas, building thriving European value chains and exploring the long-term vision for computing systems.

The central theme of this magazine is digital sovereignty. Digital sovereignty is often used interchangeably with strategic digital autonomy, but they are quite distinct. Digital sovereignty as defined in the recently signed *European Digital Sovereignty Declaration*, is a matter of authority. It is the power to govern the digital space to European values. It allows the European Union (EU) to enforce frameworks like the General Data Protection Regulation (GDPR), the Digital Markets Act, the AI Act, the Data Act, etc. While Europe excels at regulation, there is mounting geopolitical pressure to deregulate – effectively asking the EU to cede a degree of its digital sovereignty.

Conversely, strategic digital autonomy is a matter of capacity. While sovereignty provides the legal authority, autonomy provides the 'muscle' – the ability to act independently by reducing strategic dependencies. This involves, for example, building the 'EuroStack', a robust foundation ranging from sovereign cloud infrastructure and high-performance computing to open-source ecosystems and semiconductors, ensuring that European laws are backed by the technical capability to implement them.

This distinction is crucial for our community: if Europe depends entirely on foreign proprietary hardware or black-box algorithms, its legal sovereignty is undermined by technical dependence. While the HiPEAC community may have limited influence over legal frameworks, we play a vital role in strengthening Europe's strategic digital autonomy by staying on top of the digital evolution.

Building the EuroStack is a vital step toward strategic autonomy, but it is not a destination. The US and China already have their own stack; building ours will at best allow us to catch up, but it will not allow us to lead. To compete in 2035 and beyond, we must look past today's requirements. Since the future is inherently unpredictable, our best path forward is an antifragile strategy: cultivating a generation of innovators and an entrepreneurial ecosystem that thrives on volatility. By transforming Europe into a 'startup continent' by 2040, we ensure that we don't just survive the coming geopolitical storms but grow stronger because of them.

My wish for Europe in 2026 is that it takes steps to massively unleash the creativity and entrepreneurship of its citizens. By facilitating this talent, we do more than just secure our autonomy and sovereignty – we will build a more resilient, prosperous society and consolidate Europe’s position as the best continent on Earth to live, work, and run a business.

Koen De Bosschere, HiPEAC coordinator

A well-known figure in the computer-architecture community, HiPEAC 2026 keynote speaker Michaela Blott is a senior fellow at AMD with over 25 years of leading-edge computer architecture and advanced field-programmable gate array (FPGA) and board design. We caught up with Michaela in advance of the HiPEAC conference to find out about why she's passionate about computer architecture, her top trends to watch, and how AMD is focused on ever-more efficient technology for artificial intelligence (AI).

---

## **'Pairing novel algorithms with custom hardware architectures could enable step-change improvements in model capability, energy efficiency and performance'**

*What got you into computer architecture, and what keeps you passionate about the field?*

Since university, I've always enjoyed gaining a deep understanding of everything, from the application all the way down to the transistor level. That, combined with a passion for building the best possible solution to a given problem, naturally led me to designing custom compute architectures early on, three decades ago. At the time, this was a niche focus, but custom hardware architectures are increasingly becoming mainstream.

The recent surge in demand for computing power and memory, particularly due to AI workloads, combined with technological constraints and customer challenges around monetizing high-cost inference, has accelerated this shift. Custom hardware architectures are exceptionally well suited to address these evolving industry requirements.

---

***"The recent surge in demand for computing power and memory has accelerated the shift to custom hardware architectures"***

---

*Which of your professional achievements are you most proud of, and why?*

That would be FINN, a project focused on creating highly customized inference accelerators on FPGAs which we started almost 10 years ago. It can autogenerate a dataflow architecture and was originally developed for fully binarized neural networks, delivering significant performance improvements over conventional AI accelerators.

We've since expanded it to support a range of custom data types, both integer and floating point, and we are currently combining this with the former Microsoft Brainwave team to explore optimized transformer accelerators.

*What key trends in computer architecture (and computing systems more generally) are you keeping an eye on?*

One key trend is the growing importance of densely integrated 3D-stacked memory. As compute architectures become increasingly memory-constrained, traditional dynamic random-

***“FPGAs offer the flexibility to customize architectures for specific applications, thereby enhancing efficiency and performance”***

access memory (DRAM) – including high-bandwidth memory (HBM) – is starting to show its limits in meeting the evolving capacity and bandwidth demands of AI workloads.

A second area is algorithm-level innovation, such as the resurgence of recurrent neural networks (RNNs), which may offer more scalable approaches to AI. This is an active and promising area of research, and one that compute architects should track closely.

Finally, rack-level optimization is becoming critical. As the industry moves beyond chip-level performance, the focus must shift to full-system efficiency to unlock the next wave of AI scalability.

*Graphics processing units (GPUs) are currently hogging the spotlight in AI development. What role can other processors, such as FPGAs, play?*

FPGAs offer the flexibility to customize architectures for specific applications, thereby enhancing efficiency and performance. By implementing only what is needed for a specific use case, we can avoid unnecessary passes through memory with dataflow, fuse more operators and in general process the data while it's in motion.

However, it must be said, not every workload is a good fit for FPGAs – and, likewise, not every workload is ideal for GPUs.

*Why are hardware diversity and model optimization important in AI? Can't we just keep on scaling up with GPUs and large language models (LLMs)?*

While large language models have driven remarkable progress, growing questions are emerging around their ability to generalize and understand fundamental concepts, among other things, limited by the availability of high-quality training data, and the increasing demands for compute and memory which have outpaced standard technology scaling.

This is where continued innovation will be key. Developing novel algorithms with better scaling properties – such as RNNs

*The AMD Instinct MI350 series*

– and pairing them with custom hardware architectures could enable step-change improvements in both model capability but also in energy efficiency and performance.

This may also represent a strategic opportunity, particularly for regions like Europe, to explore differentiated paths and help shape the global direction of AI development.

*Are you concerned about the environmental impact of rolling out AI? If so, what actions are your team and AMD more generally taking to address this?*

At AMD, energy efficiency has long been a guiding core design principle aligned to our roadmap and product strategy. For more than a decade, we've set public, time-bound goals to dramatically increase the energy efficiency of our products and have consistently met and exceeded those targets.

We recently surpassed our ‘30x25’ energy efficiency goal, achieving a 31.7x improvement in energy efficiency for AI and high-performance computing (HPC) processors from 2020 to 2023. Building on that success, AMD has set a new, ambitious goal: to deliver a 20x improvement in energy efficiency for AI systems at the rack level by 2030. This reflects the industry's shift from chip-level to system-level optimization and underscores our commitment to responsible, high-performance innovation.

HiPEAC 2026 keynote speaker Frank Karlitschek is the co-founder and chief executive of Nextcloud, which provides a fully open-source, on-premises content collaboration platform. Since founding the company in 2016, Frank has become a vocal advocate for European digital sovereignty, as well as for open-source and privacy-preserving technological solutions. We caught up with Frank in advance of the HiPEAC conference in Kraków to talk about meaningful digital sovereignty, what makes Nextcloud special, and what he's learned in building the business.

---

## 'With Nextcloud, we have now an alternative to the big collaboration platforms from the United States'

*What does 'digital sovereignty' mean, in your view? Why is it digital sovereignty important, both for individuals and for Europe?*

In my opinion, sovereignty means the absence of strong dependencies on third parties. The more sovereignty we gain, the more it allows us to change our software or cloud provider whenever we think it is necessary. This makes us less open to blackmail. In the end it is a question of freedom.

*What do you think needs to happen for Europe to achieve meaningful digital sovereignty? What role should companies, policy makers, etc. play in this?*

We all should act strategically and improve our digital sovereignty. Governments need to act as anchor clients for digital open-source products coming from Europe. We see a lot of political initiatives which aim for more sovereignty, but we know that these take time. It is the local private sector that has to promote our economic independence in a bottom-up approach.

---

***"Only open-source software prevents dependencies on individual providers and allows independent security audits"***

---

*Frank talking at the Nextcloud Enterprise Days Paris in November 2025*

***"The community is the engine room of our product, and generates huge value. If you put effort into your community, it is a major differentiator"***

*What role does open source play in sovereignty? Do you think open source is important for technological development in Europe? If so, why?*

Only open-source software prevents dependencies on individual providers and allows independent security audits. Everyone can take the source code and build its own solution if he or she wants to. If your cloud or software provider increases the prices, you can run it on your own servers. If you are not happy with what the provider does, you can take it and fork the project. You will always have the full choice of options.

In addition, you can rely on a community which has a constant eye on the code, improves it and spots vulnerabilities very quickly.

*What inspired you to start Nextcloud? What makes Nextcloud unique, and why would you encourage people to use it?*

I have been working with open source for over 25 years now and always wanted to create something that gives people back the control over their data. With Nextcloud, we have now an alternative to the big collaboration platforms from the United States. The main differentiator is that Nextcloud is 100% open source. For anyone who thinks data privacy is important, Nextcloud is the tool they should use.

*What have you learned during the process of building the company?*

There are a lot of important learnings, but I will pick three of them. First, I think it is important to have an ethical purpose for the company and not only increase shareholder value. This keeps you and your employees motivated even during rough

*The Nextcloud Community Conference in September 2025*

seas and helps to build up a sustainable business. Second, in the open-source world the business model is an important choice to make. For us, the only feasible model is to sell enterprise subscriptions, as this does not compromise open source. The third learning is to value the community. It is the engine room of our product, and generates huge value. If you put effort into your community, it is a major differentiator.

*What are the characteristics of your ideal cloud services, from the user perspective?*

The core idea of the internet is decentralization. I think the perfect cloud service would need to work this way, too. You should be able to host software on your own server if you want to but collaborate with others through federation. Nextcloud, for example, is hosted on over 500,000 servers across the internet.

The second core aspect is open source. If you know the source code, you have the full control, and that is what counts.

*What changes would you like to see in the technology sector in Europe 10 years from now?*

We should start to value our own technology industry and stop saying that Europe can't do it. There are plenty of great tech companies which deliver alternatives to US products. If Europe had faith in its own solutions, this would be a huge push for our innovation ecosystem. Politicians can make a massive difference by actively advocating for open source and governments who implement it.

HiPEAC 2026 keynote speaker Deming Chen is the Abel Bliss Professor in the Grainger College of Engineering at the University of Illinois Urbana-Champaign. His research interests include machine learning and AI, system-level design methodologies, hybrid cloud systems, security and confidential computing, and reconfigurable and heterogeneous computing, and he has won multiple recognitions for his work. In this in-depth interview, he reflects upon major shifts in computer architecture and hardware design over the last 25 years, considers the impact of machine learning on hardware design, and discusses the demands artificial intelligence (AI) workloads are placing on hardware.

## 'While AI-assisted hardware design is far from a solved problem, it is well positioned to fundamentally reshape how hardware systems are conceived, built, verified, and deployed'

*What are some of the most profound changes in the fields of computer architecture and hardware design that you've witnessed so far in your career?*

The most profound shift I have witnessed over the past 25 years is the transition from general-purpose computing centred on the central processing unit (CPU) to heterogeneous, accelerator-rich systems. Early in my career, architectural innovation was largely driven by instruction-level parallelism and frequency scaling. As power and memory walls became dominant constraints, the field pivoted toward specialization, reconfigurability, and energy-efficient architectures.

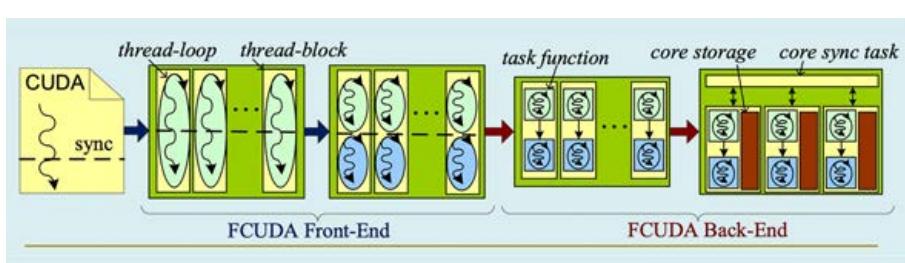

Another major change is the rise of hardware-software co-design as a necessity rather than an option. Compilers, runtimes, and architectures are now deeply intertwined, a trend reflected in my work on FCUDA, DNNBuilder, SkyNet, and ScaleHLS.

The emergence of AI has further accelerated this shift, fundamentally altering architectural priorities toward memory-centric design, data movement minimization, and domain-specific accelerators.

Equally transformative has been the rise of open-source ecosystems and deep industry-academia collaboration. Tools and ideas now propagate far more rapidly, allowing research prototypes to transition into production systems, as exemplified by the adoption of our recent work, Medusa, in NVIDIA TensorRT-LLM. At the same time, AI itself is emerging as a powerful tool for architecture and system design, reshaping how future hardware will be conceived, optimized, and validated.

*Which of your research results have had most impact?*

Several of my research contributions stand out for their sustained impact across academia and industry. FCUDA

was the first compiler framework to enable efficient translation of CUDA programs to field-programmable gate arrays (FPGAs). FCUDA created a new programming environment where both graphics processing units (GPUs) and FPGAs could be programmed using the same language in a heterogeneous compute system. This vision and effort preceded similar commercial OpenCL-to-FPGA flows offered by Intel and Xilinx by five to six years. It also significantly lowered the barrier for GPU programmers to leverage reconfigurable hardware. This work helped catalyse a broader movement toward productivity-driven accelerator design.

DNNBuilder and ScaleHLS represent another impact area. DNNBuilder enabled automated mapping of deep neural networks onto FPGAs, while ScaleHLS became the first compiler to map PyTorch models directly to customized FPGA accelerators. With thousands of downloads worldwide, ScaleHLS has influenced both research workflows and industrial prototyping.

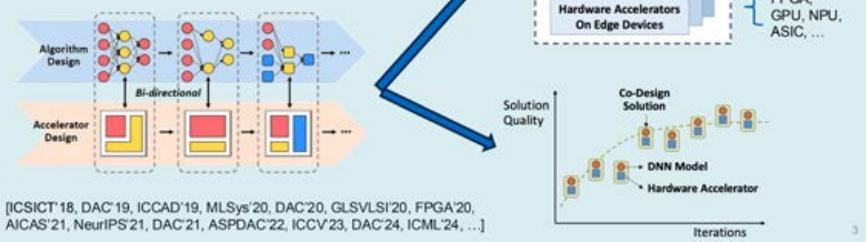

As mentioned above, Medusa's integration into NVIDIA TensorRT-LLM, delivering up to 3.6× inference speedup, exemplifies successful translation from research to production. Also, my A3C3 methodology

*FCUDA was the first compiler framework to enable efficient translation of CUDA programs to FPGAs*

(AI Algorithm and Accelerator Co-design, Co-search, and Co-generation) has had lasting influence by framing AI and hardware as co-evolving artefacts rather than separate optimization targets. Following the A3C3 design methodology, we developed the SkyNet model, which won double championships in 2019 in the DAC System Design Contest for both GPU and FPGA tracks for low-power image object detection, outperforming 100+ competitors worldwide. Later, SkyNet has been used by many other contestants and several companies.

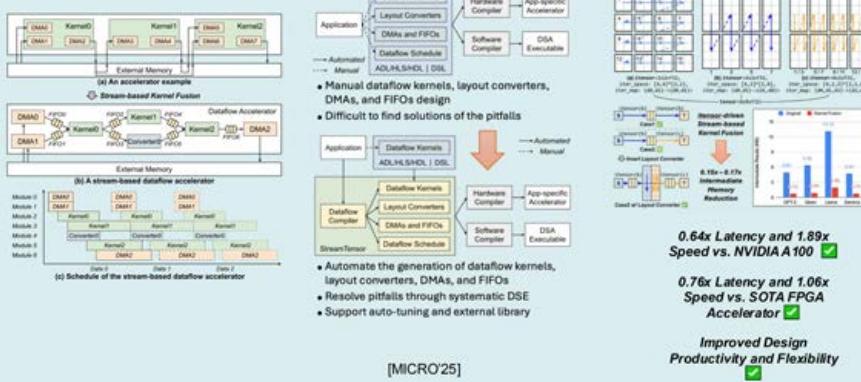

Finally, the startup company I co-founded, Inspirit IoT, Inc., recently launched a product called StreamTensor, a compiler framework that tackles the data-movement problem in AI hardware by transforming PyTorch models into optimized dataflow implementations. It includes a novel iterative tensor (itensor) type that systematically encodes stream information, describing how data moves, while the compiler identifies optimal tensor tiling, kernel fusion, and hardware-resource allocation. Based on FPGA evaluations on large language models (LLMs), StreamTensor achieves up to 0.64x lower latency and up to 1.99x higher energy efficiency compared to GPUs.

*What impact has the application of machine learning to the design of hardware had? What are some of the promises and perils of AI in hardware design and computing systems more generally?*

This is a very timely question. Machine learning (ML) has begun to meaningfully influence hardware design by introducing data-driven techniques into design space exploration, hardware code generation, and system- and tool-flow optimization. In my own work, ML-based methods have been applied to accelerator selection, high-level synthesis optimization, and scheduling decisions, enabling systems to adapt more effectively to workload characteristics and design constraints. Although these approaches are still at

### A<sup>3</sup>C<sup>3</sup> – AI Algorithm & Accelerator Co-design, Co-search, and Co-generation

- Both the AI algorithm and accelerator design spaces are **parameterized** and **co-searched** simultaneously (e.g., through gradient descent).

- Both the AI model and its accelerator are **co-generated** as a friendly pair.

*The A3C3 promotes hardware-software co-design for holistic optimization*

### StreamTensor: Make Tensors Stream in Dataflow Accelerators – Automated PyTorch-to-LLM Accelerator Generation

*StreamTensor, a commercially available product from Inspirit IoT, compiles PyTorch LLM models into stream-oriented dataflow designs for FPGAs*

an early stage, they already demonstrate strong potential to augment human expertise and significantly improve design productivity.

At the same time, substantial challenges remain. High-quality industrial design data suitable for training ML models is often scarce or proprietary, which limits model robustness and generalization. Hardware code generated by AI today can be incomplete or error-prone, raising serious concerns about correctness, verification, and trustworthiness. In addition, AI-driven design tools can make internal design decisions less transparent, complicating debugging, validation, and security assurance.

Recognizing both the promise and the challenges, in 2024 I co-founded the first IEEE International Workshop on LLM-Aided Design (LAD) together with Dr Ruchir Puri of IBM, which evolved into the inaugural IEEE International Conference on LLM-Aided Design in 2025. This venue focuses on leveraging LLMs to assist the design of circuits, software, and computing systems with improved quality, productivity, robustness, and cost efficiency. The conference has attracted hundreds of researchers and practitioners, many from industry, and has emerged as a highly impactful and promising forum. Looking ahead, while AI-assisted hardware design is far from a solved problem, it is well positioned

to fundamentally reshape how hardware systems are conceived, built, verified, and deployed, provided these challenges are addressed through careful co-design, rigorous verification, and responsible deployment.

*What are the most important requirements hardware must respond to in the AI era? How has this affected your approach to hardware design?*

In my view, hardware in the AI era must address three dominant requirements: energy efficiency, memory efficiency, and adaptability. Modern AI workloads are increasingly memory bound, driven by massive parameter counts and the cost of data movement rather than raw computation. This shift has elevated the importance of memory-centric designs, near-memory computing, dataflow-based architectures, and high-bandwidth interconnects. As noted above, our recent work, StreamTensor, the first compiler to map PyTorch LLM models directly onto FPGAs, demonstrates substantial latency and energy efficiency gains by generating custom dataflow-based LLM accelerators that significantly reduce data movement (see StreamTensor figure on p.9). This approach has already gained notable traction in both industry and the research community.

Adaptability is equally critical. AI models evolve over a timescale of months, while hardware platforms evolve over years. This mismatch has reinforced my focus on reconfigurable and programmable architectures and compiler-driven specialization. My work on FPGA-based accelerators, heterogeneous systems, and dynamic reconfiguration reflects the need to maintain flexibility without sacrificing efficiency, allowing hardware to keep pace with rapidly evolving AI algorithms.

Finally, energy efficiency and scalability now dominate system-level design in the AI era. Hardware must operate efficiently from edge devices to large-scale data centres under strict power and thermal constraints. These realities have pushed my research toward cross-layer co-design, where algorithms, compilers, hardware, and systems are optimized jointly to maximize intelligence per joule rather than peak throughput. In this context, I recently planned and co-organized the National Science Foundation workshop 'AI+HW 2035: Shaping the Next Decade' and am contributing to a vision paper outlining a 10-year roadmap toward achieving a 1000 $\times$  improvement in AI training and inference efficiency through deep

integration across abstraction layers involving both AI model and hardware (HW) innovations.

*What role do you think open source will play in hardware development in the future?*

Open source will play a foundational role in the future of hardware development, much as it has in software. As hardware systems become increasingly complex and heterogeneous, no single organization can innovate effectively in isolation. Open-source tools, benchmarks, and infrastructure enable shared progress, reproducibility, and rapid iteration across the community.

My own work reflects this philosophy. Our open-source frameworks such as FCUDA, DNNBuilder, ScaleHLS, SkyNet, CSRNet, and Medusa have achieved broad adoption, fostered community-driven improvement, and delivered real-world impact. These platforms also serve as powerful educational resources, helping train the next generation of researchers and engineers in modern hardware-software co-design practices.

Looking ahead, open source will be essential for addressing AI-era challenges. For both government and industry, open ecosystems reduce risk, avoid vendor lock-in, and accelerate workforce development. Through my leadership roles in the IBM-Illinois Discovery Accelerator Institute and the AMD Center of Excellence, I actively promote and support researchers in building and sustaining open-source ecosystems that deliver lasting impact to industry and society.

*The NSF AI+HW 2035 workshop featured a keynote by Yann LeCun and leading researchers from academia and industry, including HiPEAC associate members Kunle Olukotun and Subhasish Mitra*

# Witamy w Krakowie! Welcome to Kraków!

HiPEAC 2026 General Chair Tomasz Kryjak (AGH University of Krakow) gives us a glimpse into this year's conference's beautiful host city.

## *Why is Kraków a good location for the HiPEAC conference?*

Kraków, the former capital and second-largest city of Poland, is home to leading Polish universities and research institutes, including the Jagiellonian University, AGH University of Krakow, Cracow University of Technology, and Kraków University of Economics. Together, they conduct internationally recognized research in computer architecture, embedded systems, artificial intelligence (AI), and software engineering – areas that closely align with HiPEAC's core focus.

Kraków also hosts ACK Cyfronet AGH, Poland's leading high-performance computing centre, which plays a key role in European research infrastructures, supports large-scale simulations and data-intensive research, and currently runs the Gaia AI Factory project. In addition, the city has a vibrant ecosystem of research and development (R+D) centres and technology startups, making it a natural meeting point for academia and industry.

*Tell us about the local computing ecosystem.* Kraków hosts a large number of high-tech R+D centres operated by major international companies, including Google, IBM, Cisco, Ericsson, Nokia, Aptiv, ABB, Hitachi, Honeywell, Woodward, Genetec, Arteris and Comarch. This industrial base is complemented by local innovation drivers such as the Kraków Technology Park, startup accelerators, and specialized

ecosystems focused on 5G, the internet of things (IoT), and smart technologies, which help translate academic research into real-world applications and foster cross-sector collaboration. In addition, Kraków hosts a growing number of startups operating across the broader computing ecosystem. Ultimately, however, the city's most valuable asset is its talented pool of young people, who, after completing their education at Kraków's universities, actively contribute to and sustain the local and international R+D ecosystem.

## *What initiatives at your university would you highlight?*

A significant proportion of research initiatives focus on artificial intelligence. At the heart of this is ACK Cyfronet AGH with the Gaia AI Factory, which provides the high-performance computing infrastructure essential for AI-driven research across disciplines. At AGH University of Krakow, numerous research groups explore different aspects of AI, including the Center of Excellence in Artificial Intelligence, while at the Jagiellonian University, many AI-focused groups are coordinated by the recently established Jagiellonian Centre for Artificial Intelligence, fostering both foundational research and innovative applications.

In the embedded systems domain, my Embedded Vision Systems Group began with embedded vision implemented on field-programmable gate arrays (FPGAs),

and now we are expanding to new sensor modalities, including event cameras and LiDARs, while also exploring embedded control for AI-driven robotics. I strongly believe that embedded computing is a cornerstone for embodied AI – from drones and self-driving cars to walking robots – and this area is poised for rapid growth across AGH and other Kraków universities.

## *Any recommendations for things to do in Kraków?*

Very close to the conference venue, on the opposite bank of the Vistula River, lies Wawel Hill with its Royal Castle, the former seat of Polish kings and a symbol of the nation's history. From there, a pleasant walk leads to the Main Market Square (Rynek Główny), one of the largest medieval squares in Europe, home to the iconic St Mary's Basilica and the historic Cloth Hall. The nearby Kazimierz district, with its cafés, restaurants, and vibrant atmosphere, is an excellent place to continue conversations after conference sessions.

The UNESCO-listed Wieliczka Salt Mine, about 45 minutes from Kraków, offers an extraordinary underground world of tunnels, chambers, and sculptures carved entirely from salt. Nature lovers may also consider a trip to Zakopane in the Tatra Mountains. Finally, no visit to Kraków is complete without sampling traditional Polish cuisine – especially żurek soup, pierogi (dumplings), and bigos.

# Winners of the 2025 HiPEAC Technology Transfer Awards

Since 2012, the HiPEAC Technology Transfer Awards have been celebrating examples of boundary-pushing research from the HiPEAC community reaching the market. For the 14th edition, five transfers were selected for an award, three of which resulted in new European technology companies. The winners will be recognized in an awards ceremony at the HiPEAC conference in January, and first-prize winners receive a cash prize of € 1,000.

## ACE3: Democratizing large-scale AI through groundbreaking software acceleration

Xiaoyang Sun, University of Leeds, UK

ACE3 is an advanced software platform that removes memory bottlenecks in hardware accelerators, enabling training of large AI models without massive supercomputing resources.

Large neural networks often hit hardware limits, as even powerful accelerators are constrained by memory bandwidth and capacity. ACE3 addresses this with a software-based acceleration technique that optimizes data handling and load balancing across heterogeneous compute units, unlocking more performance from existing hardware and enabling much faster training of complex AI models without new specialized accelerators.

After being commercialized through a spinoff company, ACE3 AI LTD, this technology is now available through a user-friendly platform that delivers these optimizations to industry and research teams. In partnership with industries, the ACE3 platform has shown significant reductions in training time and computing costs on real-world workloads. ACE3 AI LTD's broader vision is to democratize advanced AI by easing hardware constraints and enabling more organizations to use state-of-the-art models without massive infrastructure investments.

The ACE3 team members are Dr. Xiaoyang Sun, Professor Jie Xu, and Professor Zheng Wang.

ACE3 website: [ace3ai.com](http://ace3ai.com)

Xiaoyang Sun's website: [xshaun.github.io](http://xshaun.github.io)

Jie Xu's webpage on the University of Leeds website:

[eps.leeds.ac.uk/computing/staff/331/professor-jie-xu](http://eps.leeds.ac.uk/computing/staff/331/professor-jie-xu)

Zheng Wang's website: [zwang4.github.io](http://zwang4.github.io)

## Belfort: Hardware acceleration for computing on encrypted data

Ingrid Verbauwhede, KU Leuven / Belfort, Belgium

Belfort is a new KU Leuven spinoff. It has launched the world's first available product that accelerates encrypted compute in hardware, making it possible to process encrypted data without ever decrypting it. It allows servers to compute directly on encrypted inputs, so sensitive information is never exposed, even during execution. Historically, this approach has been too slow and costly for real-world use. With Belfort's custom hardware architecture, encrypted compute is now viable in real time for the first practical workloads. From fraud detection to genomic analysis, privacy-preserving applications are moving from theory to reality.

Belfort is a spinoff from KU Leuven's COSIC (Computer Security and Industrial Cryptography) lab, a global leader in secure computation and cryptographic hardware. The research underpinning Belfort's core technology was developed over several years, and matured through several grants and research projects, including two grants from the European Research Council.

Belfort website: [belfortlabs.com](http://belfortlabs.com)

COSIC lab: [esat.kuleuven.be/cosic](http://esat.kuleuven.be/cosic)

*The Belfort founding team: Laurens De Poorter (COO), Furkan Turan (Head of Engineering), Michiel Van Beirendonck (CEO) and Ingrid Verbauwhede (Head Scientist). Photo by Fred Paulussen (Fredography)*

## Accelerating early software development: A high-performance parallel hardware-simulation framework

Nils Bosbach, RWTH Aachen University, Germany

The Institute for Communication Technologies and Embedded Systems (ICE) at RWTH Aachen University has transferred a parallelization and co-simulation technology for SystemC-based virtual prototypes to MachineWare GmbH. The package combines a generic intra-process parallelization strategy for virtual central processing unit (CPU) models with a multi-process co-simulation orchestration layer. Integrated into MachineWare's ecosystem, the technology delivers faster virtual-platform execution, enabling broader CI/regression coverage, earlier bug discovery, and more efficient pre-silicon software development for heterogeneous system-on-chips (SoCs).

MachineWare website: [machineware.de](http://machineware.de)

ICE RWTH Aachen website: [ice.rwth-aachen.de](http://ice.rwth-aachen.de)

## Novel intermediate representation for efficient recursive query processing

Amir Shaikhha, University of Edinburgh, UK

Recursive query processing underpins a broad range of applications – from databases and knowledge-graph management to declarative networking, artificial intelligence, and machine learning. This knowledge transfer involves a novel intermediate representation (IR) for recursive queries, called TempoDL, together with its associated compilation and optimization techniques, introduced in ‘Optimizing Nested Recursive Queries’ (SIGMOD 2024). This transfer enables the direct incorporation of TempoDL and its associated compilation pipeline, developed in collaboration between the University of Edinburgh and RelationalAI, into an industrial relational knowledge-graph platform, allowing customers to express rich, recursive business logic with production-grade performance, scalability, and semantic guarantees.

University of Edinburgh Informatics website:

[informatics.ed.ac.uk](http://informatics.ed.ac.uk)

RelationalAI website: [relational.ai](http://relational.ai)

## Ximplic: Simplifying computing-in-memory

Simranjeet Singh and Farhad Merchant, University of Groningen, The Netherlands

The embedded system-on-chip (SoC) market is rapidly expanding, driven by the need for compact, energy-efficient, and high-performance computing solutions

across sectors such as edge AI, the internet of things (IoT), automotive, and industrial automation. Valued at USD 169.5 billion in 2023 and projected to reach USD 295.5 billion by 2030 (CAGR  $\approx$  8.5%), this market's growth is increasingly constrained by the traditional von Neumann bottleneck, where excessive data movement between memory and processor dominates energy consumption and latency.

Computing-in-memory (CiM) directly addresses this limitation by integrating computation within memory arrays, thereby minimizing data transfer, enhancing parallelism, and enabling orders-of-magnitude improvements in energy efficiency. From a market-demand perspective, embedding CiM functionality into SoCs offers a disruptive advantage for real-time AI inference, sensor-edge processing, and low-power autonomous systems. As major semiconductor companies and startups alike invest in CiM-enabled architectures, the technology is poised to redefine the performance-efficiency balance of embedded SoCs and capture a significant portion of this rapidly growing market.

However, a major challenge in deploying CiM architectures lies in the extended development cycle associated with their complex integration into SoCs. To address this critical bottleneck, Farhad Merchant, and Simranjeet Singh, researchers at the University of Groningen, have founded a spinoff company, Ximplic, dedicated to accelerating the design of computing-in-memory architectures through advanced electronic design automation (EDA) tools and intellectual property blocks (IPs).

Ximplic's EDA platform and IPs tackle these challenges with a device-agnostic ecosystem tailored for CiM workflows. It supports any underlying device technology while unifying modelling, simulation, logic synthesis, and hardware prototyping within a single intelligent environment. Designers can seamlessly move from concept to silicon, independent of the memory technology, enabling rapid exploration and implementation. By simplifying complexity across the entire hardware design flow, Ximplic empowers faster innovation from device physics to system-level realization, paving the way for the next generation of energy-efficient, memory-driven computing.

Ximplic website: [ximplic.com](http://ximplic.com)

Groningen Cognitive Systems and Materials Center (CogniGron) website:

[rug.nl/research/fse/cognitive-systems-and-materials](http://rug.nl/research/fse/cognitive-systems-and-materials)

# Lakeside Lab researchers announce Swarmtelect spinoff

Researchers at Austria's Lakeside Labs have announced a future spinoff, Swarmtelect.

Swarmtelect offers intelligent workload allocation and orchestration solutions that use decentralized swarm intelligence to optimize complex systems like production lines, edge-fog-cloud computing environments, and energy networks. It provides autonomous decision-making, predictive resource allocation, and self-healing capabilities that the researchers say keep systems running smoothly even during disruptions, while integrating seamlessly with existing infrastructure.

'What really sets Swarmtelect apart is its focus on decentralized collective intelligence. Instead of relying on a central controller, systems can self-organize and adapt in real time. On top of that, we offer explainable resource management and turn advanced research into solutions that actually work

in real industrial environments,' says Marija Gojkovic, one of Swarmtelect's founders.

'Swarmtelect is the result of a full year of sharpening an idea we truly believe in: making decentralized swarm intelligence practical, reliable, and ready for real-world infrastructures. What started as research has matured into a solution that can autonomously orchestrate resources where complexity is the norm. I'm excited to finally take this step from theory to impact,' added co-founder Melanie Schranz, a member of the DISCOVER-US network.

The founders of Swarmtelect – Melanie Schranz, Marija Gojkovic, Péter Forgács and Khalil Al-Rahman Youssefi – are open to partnerships, pilots, and collaborations.

[swarmtelect.com](http://swarmtelect.com)

[linkedin.com/company/swarmtelect](https://linkedin.com/company/swarmtelect)

# Anyway Systems spun off from EPFL's Distributed Computing Lab

Anyway Systems, recently spun off from EPFL's Distributed Computing Lab (DCL), is commercializing software that eliminates the need for data to be sent to third-party cloud services when artificial intelligence (AI) is used to complete a task. Developed by EPFL researchers Gauthier Voron, Geovani Rizk and Rachid Guerraoui, the software allows users to download open-source AI models and use them locally.

According to the launch announcement by EPFL, Anyway Systems combines distributed machines on a local network into an on-premise cluster. It uses robust self-stabilization techniques to optimize the usage of underlying local hardware. The researchers say that this means that huge AI models can be deployed on Anyway Systems in a few minutes, requiring no more than four machines with one commodity graphics processing unit (GPU) each.

'For years people have believed that it's not possible to have large language models (LLMs) and AI tools without huge resources, and that data privacy, sovereignty and sustainability were just victims of this, but this is not the case and smarter,

frugal approaches are possible,' said Rachid Guerraoui, head of the DCL.

'Anyway Systems represents an interesting technology that optimizes resource usage while ensuring data security and sovereignty,' said HiPEAC member David Atienza, associate vice-president of research centres and technology platforms at EPFL. 'Its sustainable approach aligns perfectly with the needs of EPFL's advanced computing platforms and will play a pivotal role in shaping the trajectory of future AI development at EPFL to consume fewer resources with the deployment of LLMs such as Apertus.'

Anyway Systems was recently chosen as one of six inaugural grantees of the Startup Launchpad AI Track – powered by UBS. The software is currently being tested in companies and administrations across Switzerland.

Announcement on EPFL website:

[go.epfl.ch/d8e896](http://go.epfl.ch/d8e896)

[anyway.dev](http://anyway.dev)

[linkedin.com/company/swarmtelect](https://linkedin.com/company/swarmtelect)

## Cloudberry announces Europe-focused semiconductor VC fund

Venture capital (VC) firm Cloudberry, which is based in Helsinki and London, has launched a fund of €30 million, which will be dedicated to semiconductors, photonics, and advanced materials startups. The fund will invest at pre-seed and seed stages, focusing on technologies linked to compute, connectivity, sensing, and power. Cloudberry is backed by Finnish state-owned investment company Tesi and partners including Global Foundries and Radiant Opto-Electronics.

According to the press release announcing the launch, the team plans to invest in up to 20 companies across Europe, ranging from early research and development (R+D) spinouts

to teams commercializing innovations within the fund's core focus areas.

'We see this as the start of a long-term effort to build Europe's semiconductor ecosystem,' said Veera Pietikäinen, founding partner at Cloudberry. 'Europe has world-class talent and deep technology capabilities in semiconductors and photonics, but has lacked investors who truly understand how to support and scale them. We are now building a specialist platform that helps these companies grow and strengthen Europe's technological sovereignty in the process.'

↗ [cloudberry.vc](http://cloudberry.vc)

## Embedded IoT cybersecurity scaleup Exein raises €170m in 2025

Exein, a company providing embedded internet-of-things (IoT) cybersecurity solutions, recently announced a successful €100 million funding round, bringing the total raised by the company in 2025 to €170 million. Founded in 2018 and headquartered in Rome, Exein also has offices in Germany, Taiwan, and the United States.

Exein's solutions embed advanced security directly into device software, leveraging edge artificial intelligence for real-time threat detection and response. Announcing the funding

round, Exein stated that the new investment will support their mergers and acquisitions (M&A) strategy as the company continues scaling across new markets and launch their next-generation technology in 2026.

The round was led by Blue Cloud Ventures, joined by HV Capital, Intrepid Growth Partners, Geodesic Capital and the investment bank J.P. Morgan.

↗ [exein.io](http://exein.io)

↗ [linkedin.com/company/exein](http://linkedin.com/company/exein)

## NobodyWho raises €2 million in pre-seed funding for on-device inference engine

Copenhagen-based startup NobodyWho recently announced that they have raised €2 million in pre-seed funding to bring smaller artificial intelligence (AI) models directly onto users' devices. Founded by entrepreneur and artist Cecilie Waagner Falkenstrøm, along with co-founder and chief technology officer Asbjørn Olling, NobodyWho's open-source inference engine enables small language models (SLMs) to run locally on laptops and mobile phones, meaning that data does not have to leave the device.

Announcing the funding round on LinkedIn, Cecilie Waagner Falkenstrøm said: 'We began challenging the "bigger-is-better" logic of cloud AI and pushing toward another future – one where AI runs on-device, works offline, respects privacy and data sovereignty, and is far more cost-efficient and climate-aligned.'

The funding round was backed by Nordic early-stage investors PSV Tech and The Footprint Firm, with participation from Norrsken Evolve.

↗ [nobodywho.ooo](http://nobodywho.ooo)

# Wodan AI closes €2 million pre-seed round for encrypted AI technology

Wodan AI, a Spanish-Belgian startup, recently announced a successful €2 million pre-seed funding round. According to the company website, Wodan AI enables secure, privacy-preserving artificial intelligence (AI) by converting standard models into encrypted runtimes using homomorphic encryption (HE). The platform combines advanced cryptography with containerized orchestration to keep data private, including during computation.

The funding round was led by Spanish venture capital firms JME Ventures, Swanlaab, and Adara Ventures, with additional backing from Belgium-based ScaleFund, the company announced this week.

According to a report in Tech Funding News, Wodan AI is relocating its global headquarters to Madrid and consolidating its research and development (R+D) operations in Spain. 'Spain has the technical talent required to develop critical sovereign AI technologies. With our headquarters, R+D centre and team growth in Madrid, we aim to consolidate a European hub of reference in private, secure AI designed for the most demanding sectors,' the report quotes Manuel Pérez Yllan, chief technology officer and co-founder of Wodan AI, as saying.

[wodan.ai](http://wodan.ai)

[techfundingnews.com/wodan-ai-2m-encrypted-ai-europe/](http://techfundingnews.com/wodan-ai-2m-encrypted-ai-europe/)

# S2C, MachineWare and Andes launch RISC-V co-emulation solution

S2C, MachineWare, and Andes Technology recently announced a collaborative co-emulation solution designed to address the increasing complexity of RISC-V-based chip design. The solution integrates MachineWare's SIM-V virtual platform, S2C's Genesis Architect and Prodigy FPGA prototyping systems, and Andes' high-performance AX46MPV RISC-V CPU core, providing a unified environment for hardware and software co-verification.

Announcing the solution, MachineWare noted that as RISC-V designs move toward high-performance, multicore, and highly customized architectures, pre-silicon software development and system validation have become more challenging.

The announcement states that this solution supports a 'shift-left' verification approach, allowing hardware and software teams to work in parallel, resulting in reduced development time and lower project risk.

Based in Aachen, MachineWare was launched with its high-speed functional RISC-V simulator, SIM-V, in 2022. Its founders form part of the HiPEAC network.

[machineware.de](http://machineware.de)

[s2cinc.com](http://s2cinc.com)

[andestech.com](http://andestech.com)

# Launch of Sainet: Siena Artificial Intelligence Network

**Siena Artificial Intelligence Network**

Launched at the end of 2025, Sainet is a not-for-profit initiative creating a community around artificial intelligence in Siena, Italy. Co-founded by Pietro Pianigiani, currently working on hardware at the Barcelona Zettascale Lab founded by Barcelona Supercomputing Center, Sainet

is linked to the University of Siena and SAILab, the local artificial intelligence lab. Sainet aims to promote knowledge-sharing, startup acceleration and community building, with a particular focus on education and technology transfer.

[sainet.it](http://sainet.it)

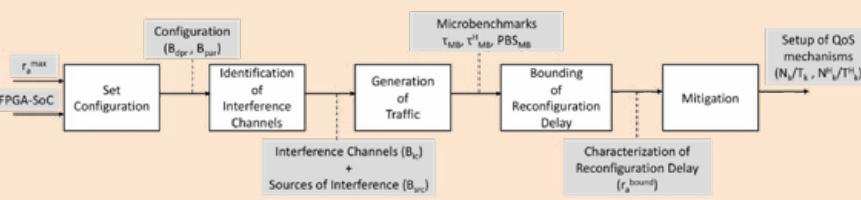

## New paper enables predictable reconfiguration in safety-critical systems

Giacomo Valente,

University of L'Aquila

Researchers from the University of L'Aquila and Collins Aerospace have developed a new approach that enables embedded systems to meet strict size, weight, and power (SWaP) constraints while maintaining real-time high performance. Their work, titled 'Leveraging Traffic Injection and Quality-of-Service to Control the Reconfiguration Delay', focuses on systems based on runtime reconfigurable hardware and addresses one of their most persistent challenges: the variability of reconfiguration delay.

Many advanced systems use dynamic reconfiguration to swap hardware modules on the fly. This allows multiple accelerators to share the same field-programmable gate array (FPGA), helping to meet SWaP constraints. However, the time needed to load a new module, the reconfiguration delay, is notoriously unpredictable because it depends on interference from other components accessing shared resources such as memory or communication buses. This unpredictability significantly complicates the adoption of dynamic reconfiguration in safety-critical contexts, including aerospace systems. Existing solutions to bound this delay typically require additional hardware, intrusive architectural changes, or impose performance penalties on other tasks.

The new approach instead takes advantage of what modern systems-on-chip already offer. By accurately modelling the interference generated by concurrent tasks and exploiting built-in quality-of-service (QoS) mechanisms, the approach provides designers with a safe and tight upper bound on reconfiguration delay, without adding hardware or consuming extra system resources.

The researchers validated their solution on a Xilinx Zynq UltraScale+ platform through two extensive experiments. In uncontrolled conditions, reconfiguration delay was predicted to increase up to 6.3 $\times$  compared to isolation. With the proposed QoS configuration, automatically generated by their tool, the delay remained strictly bounded to 1.8 $\times$ , while competing tasks experienced only a 14% slowdown. This represents a substantial improvement over existing approaches.

By making runtime reconfiguration predictable using standard architectural features, this work strengthens timing assurance in safety-critical systems across domains such as aerospace, robotics, and autonomous vehicles.

### FURTHER INFORMATION:

G. Valente, V. Muttillo, F. Federici, L. Pomante, T. Di Mascio, 'Leveraging Traffic Injection and Quality-of-Service to Control the Reconfiguration Delay', *Journal of Systems Architecture*, Volume 168, 2025, DOI: 10.1016/j.sysarc.2025.103570

[doi.org/10.1016/j.sysarc.2025.103570](https://doi.org/10.1016/j.sysarc.2025.103570)

## Jeronimo Castrillón awarded ERC Consolidator

HiPEAC member Jeronimo Castrillón Mazo, Chair of Compiler Construction at the Faculty of Computer Science at TUD Dresden University of Technology (TUD), has been awarded a European Research Council (ERC) Consolidator Grant. His project, COMpilers for ExTreme Heterogeneity (COMETH), which will run for five years and receive €2 million in funding, aims to develop a new generation of tools that will simplify the programming of increasingly complex computer systems.

As new technologies emerge, such as in-/near-memory computing or quantum computing, computers are set to combine many fundamentally different types of hardware. This makes programming considerably more difficult. The COMETH project is building models capable of understanding different computing paradigms and knowing how they can work together to solve a task, allowing complex programming code to be automatically translated into the detailed instructions required by computers.

[bit.ly/TU\\_Dresden\\_COMETH](https://bit.ly/TU_Dresden_COMETH)

The five steps of the proposed approach

# New architecture developments discussed at REACH 2025 in London

Sarah Sennett, Institute of Engineering and Technology

‘An architectural framework is for life, not just for Christmas!’ So said Arm’s Executive Vice President and Chief Architect, Richard Grisenthwaite, as he delivered the opening keynote at REACH 2025 – the Institution of Engineering and Technology’s computer architecture conference, now in its second year.

Richard’s talk looked at how computing, and Arm’s technology, will develop in view of the rise of artificial intelligence (AI) and machine learning. He predicted that the future will include very specific AI, used to solve very specific problems, and that finely targeted systems will be more efficient than large data centres. AI has expedited the range of systems that can be developed; however, innovation will be determined by the trust in the systems that they run on.

AI was a common theme over the two days of the conference. Michaela Blott (AMD) – also the HiPEAC 2026 opening keynote speaker – noted that the evolution of AI is accelerating, and highlighted some of the challenges presented. Agility – and accelerated accelerator development – will be key to resolving the challenges, she said. In his talk, Jangwoo Kim (MangoBoost), explored how modern datacentre and server architectures are being reshaped by the increased use of AI. Smart network scaling will be the key, he said.

The topic of AI was continued in a panel discussion titled ‘The Chip Architecture for Future AI – Does it Exist?’, which included contributions from Sophie Wilson CBE (Broadcom), Karu Sankaralingam, (NVIDIA), Partha Maji (Microsoft), Atiq Bajwa, (Ampere Computing), Carlo Luschi, (Graphcore), and Wayne Luk (Imperial College London).

Panel session at REACH 2025

Sustainability in computer design was another important topic discussed. HiPEAC member Lieven Eeckhout (Ghent University) pointed out that we need to reduce device carbon emissions by 15.5% per device, per year, to meet the Paris Agreement for carbon reduction. However, the transition to green energy is not moving fast enough.

How will computer architecture develop over the next 25 years? Boris Grot (University of Edinburgh), a HiPEAC member and member of the REACH organizing committee, posed the question of what the sector will look like in 2050 in an interactive panel session. The panel’s thoughts included:

- More customized processors for defined tasks – Richard Grisenthwaite (Arm)

- Lots of opportunity to rethink memory as a system that can process – Onur Mutlu (ETH Zürich)

- Generative AI is going to have a huge impact, including on the labour market – Karu Sankaralingam, (NVIDIA)

- Memory architectures will become more distributed. Lots more static scheduling, with associated power benefits – Chris Wilkerson (Intel)

- Data centres will grow exponentially to meet computing needs, providing 24/7 information and suggestions streams, personalized to the user’s data – Adi Yoaz (Huawei)

Closing the conference, Hidetsugu Irie (University of Tokyo) gave the first talk in Europe on the STRAIGHT architecture. This approach retains the classical sequential programming model, while reducing per-instruction renaming overheads and opening new scaling paths.

In addition to a lively lecture room, REACH 2025 featured a poster session of the latest research in computer architecture and related technologies. The best poster, as voted for by the delegates, was awarded to HiPEAC member José Cano and his student Jude Haris (University of Glasgow), for their poster ‘Accelerating AI at the Edge: The Power of Efficient HW/SW Co-Design’.

REACH 2026 will return to London in November 2026. The call for posters will open in early 2026. More information is available from [spkl.io/6005AcYi5](https://spkl.io/6005AcYi5)

## Christian Pilato appointed chair of ACM SIGDA

HiPEAC member Christian Pilato (Politecnico di Milano) has been appointed Chair of ACM SIGDA (Special Interest Group on Design Automation). In a post announcing the appointment, Christian said: 'The design automation community is evolving rapidly, driven by AI-powered design, heterogeneous computing, and the growth of open-source hardware and EDA ecosystems. Now more than ever, collaboration and inclusiveness are key to advancing our field.'

'As Chair, my focus will be on broadening SIGDA's global membership, strengthening engagement through active member contributions, bridging academia, industry, and open-source communities, and ensuring our events remain sustainable and accessible. I look forward to collaborating with colleagues and partners worldwide.'

For further information on how to get involved, visit the ACM SIGDA webpage:

[acm.org/special-interest-groups/sigs/sigda](https://acm.org/special-interest-groups/sigs/sigda)

## Koen De Bosschere admitted to Royal Flemish Academy of Belgium

HiPEAC coordinator Koen De Bosschere was formally admitted to the Royal Flemish Academy of Belgium on 20 December 2025 for his scientific and societal impact in the field of computer science. His inaugural speech in the Class of Technical Sciences was entitled 'From classroom to boardroom: the entrepreneurial ecosystem in Ghent'.

Koen De Bosschere (second from left) admitted to the Royal Flemish Academy of Belgium

## ACM Gordon Bell Prize for Climate Modelling awarded to 26-person team

Multiple European institutions represented, including HiPEAC member Torsten Hoefler's team at ETH Zürich.

The 2025 ACM Gordon Bell Prize for Climate Modelling was presented to a 26-member team for developing a full Earth simulation at 1 km resolution during the Supercomputing conference in St. Louis, Missouri, United States, in November 2025. The award honours innovative contributions to parallel computing toward solving the global climate crisis.

Announcing the award, ACM noted that, while digital simulations of the Earth are among the most effective tools to understand climate change, simulating how human activity influences the climate is an extraordinarily difficult challenge. This is due to the huge number of variables that need to be taken into consideration – such as the cycles of water, energy, and carbon, how those factors relate to each other, and how diverse physical, biological, and chemical processes interact over space and time.

The 26-member team was the first to develop a full Earth simulation at a resolution of 1 km, using compute power provided by the Alps and JUPITER supercomputers, based in Switzerland and Germany, respectively.

The team comprised researchers from the following organizations: ETH Zürich (including HiPEAC member Torsten Hoefler), Deutsches Klimarechenzentrum, NVIDIA, Max Planck Institute for Meteorology, University of Hamburg, Forschungszentrum Jülich and the Swiss National Supercomputing Centre.

[awards.acm.org/bell-climate](https://awards.acm.org/bell-climate)

### Michael O'Boyle, Michele Magno and Thomas Ernst named IEEE Fellows

The January 2026 cohort of IEEE Fellows included two HiPEAC members. The IEEE Fellow grade is conferred by the IEEE Board of Directors to individuals with outstanding qualifications and significant contributions to engineering, science, and technology.

HiPEAC founding member Michael O'Boyle (University of Edinburgh) was selected for his contributions to machine learning-based compilation and parallelization. Meanwhile, HiPEAC member Michele Magno (ETH Zürich) was recognized for his contributions to low-power wake-up radios and energy harvesting for smart sensors.

Thomas Ernst (CEA Leti), a contributor to several editions of the HiPEAC Vision, was also named IEEE Fellow for his contributions to 3D-stacked gate-all-around nanosheet and nanowire transistors.

Further information is available in the announcement by the IEEE Computer Society:

[computer.org/press-room/2026-class-fellows](https://computer.org/press-room/2026-class-fellows)

Videos of lectures by Michael O'Boyle and Michele Magno are available in the ACACES 2023 playlist:

[bit.ly/ACACES23\\_videos](https://bit.ly/ACACES23_videos)

A HiPEAC Vision webinar featuring Thomas Ernst is available in the HiPEAC webinars playlist:

[bit.ly/HiPEAC\\_webinar\\_videos](https://bit.ly/HiPEAC_webinar_videos)

### Ewa Deelman receives IEEE Sidney Fernbach Memorial Award

In November, DISCOVER-US member Ewa Deelman (University of Southern California) was named recipient of the IEEE Sidney Fernbach Memorial Award, given for outstanding contributions in the application of high-performance computers using innovative approaches. The award was made in recognition of her work in workflow-based parallel and distributed computing. Ewa leads the design and development of the Pegasus Workflow Management System, a widely adopted platform that enables large-scale, reproducible, and open computational science across domains. Her research spans workflow optimization, resource provisioning, data management, provenance capture, and the use of cloud and hybrid platforms for scientific discovery.

### Timothy Jones inducted into MICRO Hall of Fame

In October, HiPEAC member Timothy Jones was inducted into the ACM/IEEE MICRO Hall of Fame, which recognizes authors who have had eight or more papers published at the IEEE/ACM International Symposium on Microarchitecture (MICRO).

The MICRO Hall of Fame includes numerous HiPEAC members; additions in recent years include Lieven Eeckhout (Ghent University) and Stefanos Kaxiras (Uppsala University).

### MICRO Test of Time Award for Gabriel Loh and co-authors

In October, HiPEAC associate member Gabriel Loh and co-authors were awarded the MICRO Test of Time Award for their 2006 paper 'Die Stacking (3D) Microarchitecture'. The award recognizes the most influential papers published in prior sessions of the IEEE/ACM International Symposium on Microarchitecture (MICRO). The paper was selected 'for pioneering the microarchitectural evaluation of 3D die stacking, demonstrating its potential for substantial performance/power gains and shaping future 3D die-stacking research'.

## Ingrid Verbauwhede awarded FWO Excellence Prize

In a formal ceremony in November, HiPEAC member Ingrid Verbauwhede (KU Leuven / Belfort) was awarded the 2025 FWO Excellence Prize, one of the highest scientific honours in Belgium.

The prestigious award, which is awarded every five years and has a prize of €100,000, was made in recognition of Ingrid's pioneering work in hardware and semiconductor security. Ingrid is the recipient of multiple international honours, including two ERC Advanced Grants, the IEEE Don Pederson Award (2023), and the EDAA Achievement Award (2024).

[bit.ly/COSIC\\_Ingrid\\_Verbauwhede\\_FWO](https://bit.ly/COSIC_Ingrid_Verbauwhede_FWO)

## Isak Karabegović wins Lifetime Achievement Award Bosnia and Herzegovina

In December, HiPEAC member Isak Karabegović received the Federal Lifetime Achievement Award in Science for 2025, awarded by the Government of the Federation of Bosnia and Herzegovina, for his longstanding and outstanding contribution to the development of science, higher education and international cooperation.

Accepting the award, Isak thanked his collaborators and added: 'I would like to send a message to young people not to be afraid of knowledge, to take knowledge into their own hands, to be innovative and creative because our future depends on their research and work.'

[fmon.gov.ba/Obavjest/Pregled/1597](https://fmon.gov.ba/Obavjest/Pregled/1597)

## Dates for your diary

### HiPEAC webinars

Check the HiPEAC website to keep up to date on forthcoming dates

[hipeac.net/webinars](https://hipeac.net/webinars)

### DATE 2026: Design Automation and Test in Europe Conference

20-22 April 2026, Verona, Italy

[date-conference.com](https://date-conference.com)

### EuroSys 2026: European Conference on Computer Systems

27-30 April 2026, Edinburgh, UK

[2026.eurosys.org](https://2026.eurosys.org)

### ISC High Performance

22-26 May 2026, Hamburg, Germany

[isc-hpc.com](https://isc-hpc.com)

Photo credit: ItalyDrones | stock.adobe.com

### ACACES 2026: Advanced Computing Architecture and Compilation for High-performance Embedded Systems Summer School

12-18 July 2026, Fiuggi

HiPEAC summer school

Applications open March 2026

[hipeac.net/acaces/2026](https://hipeac.net/acaces/2026)

### ACM Summer School on HPC Computer Architectures for AI and Dedicated Applications

20-24 July 2026, Barcelona

Deadline for applications: 15 February

[europe.acm.org/seasonal-schools/hpc/2026](https://europe.acm.org/seasonal-schools/hpc/2026)

### NorCAS 2026: IEEE Nordic Circuits and Systems Conference

27-28 October 2026, Tampere, Finland

[events.tuni.fi/norca](https://events.tuni.fi/norca)

Special session proposals deadline: 15 June 2026

Paper submission deadline: 15 August 2026

Further information: Jari Nurmi, Tampere University

[norcas@tuni.fi](mailto:norcias@tuni.fi)

## Special feature: Digital sovereignty

Europe's technological dependencies – and their impact on the ability of the European Union (EU) to enforce its own laws – are under scrutiny. Launched in September 2024, EuroStack is an industrial-strategy project and not-for-profit foundation led by the European tech industry. HiPEAC spoke to EuroStack Chair Cristina Caffarra and Board Member Stéfane Fermigier to find out what constitutes 'digital sovereignty', why Europe should take urgent action to rebuild its technology sector, and what EuroStack is doing to address this issue.

# 'By not controlling our critical digital infrastructure, we have ceded control over our economic future and our ability to uphold our own laws and values'

While Europe's position in the information technology sector has been waning for decades, recent events have resulted in an ever-louder chorus of voices concerned about the continent's ability to control its digital destiny.

There are several pressing reasons behind this concern. First, a weak technology sector in Europe has critical consequences on the economy. 'For years, Europe has outsourced its digital foundations, becoming what many call a "digital colony". This leads to a recurrent, massive outflow of resources: a recent study estimates that European businesses' reliance on US-based cloud and software services benefits the US economy to the tune of €264 billion annually – a figure comparable to our total energy-import bill, or which represents three million jobs in Europe,' says Stéfane Fermigier, founder and chief executive of the open-source software vendor Abilian and a co-founder of the EuroStack Initiative Foundation.

The implications are grave, according to the economist and EuroStack Chair Cristina Caffarra, who agrees with the conclusions of Mario Draghi's 2024 report, *The future of European competitiveness*. 'We are an exporting economy which is being clobbered by an active trade war with China, and loss of competitiveness with both China and the United States (US). While productivity growth was similar 20 years ago between the US and Europe, there has been a major decoupling as the US pulled ahead, driven by its tech sector. Digital is – and artificial intelligence (AI) will be – an all-purpose technology. If you are behind with adoption and diffusion of these technologies, you lose out in every sector of the economy. So to me this is not remotely an anti-US campaign: US suppliers have filled a vacuum we have left for them to fill, kudos. But if we don't focus on building our own capabilities in this space, we will fall further and further behind.'

Second, recent geopolitical events have thrown Europe's vulnerability, through its reliance on imported technologies, into sharp relief. 'Global instability means that Europe can no longer take for granted the reliability of its traditional partners. Our dependencies are no longer simply a commercial issue, but a critical strategic vulnerability,' says Stéfane. There is also growing awareness of the legal and security risks that reliance on extraterritorial technology entails: 'European companies' data and intellectual property are exposed to extraterritorial laws like the US CLOUD Act and FISA, which can compel disclosure to a foreign government without regard for European privacy and business secrets standards. This is a direct threat to our competitiveness and security,' adds Stéfane.

### Defining 'digital sovereignty'

For Stéfane, digital sovereignty is 'the ability of individuals, organizations, and governments to independently control, manage, and use their digital infrastructure, data, and

Cristina Caffarra speaking at the European Digital Sovereignty Summit, November 2025

technologies, free from undue external systems in a self-determined manner'. In addition to the governance of critical infrastructure, this also entails 'the ability to make autonomous decisions about the use and management of applications and technologies, safeguarding privacy, data integrity, and digital independence'.

However, as Koen De Bosschere notes in his introduction to this magazine edition, the power to govern the digital space is dependent to a large extent on the technical capacity to implement European laws – i.e. reducing dependency on technologies from other regions. For Cristina, attempting to tame technology companies through regulation is a failed approach; the emphasis must shift to building up the technology sector in Europe. 'We are now a digital colony, because while we were busy regulating Google Search, Apple's App Store, Meta's social networks, companies were building data centres, laying cables, appropriating the data – which effectively means that the digital infrastructure we rely on today is not ours.'

Cristina fiercely rejects the negative attitude exhibited by some which suggests that Europe has missed the boat on technological development – noting that Europe has 'incredible capabilities, incredible assets, some of the best engineers', with dynamic ecosystems – even for chips – in places like Dresden, Eindhoven, and Grenoble – but laments that Europeans are 'complacent beyond words'.

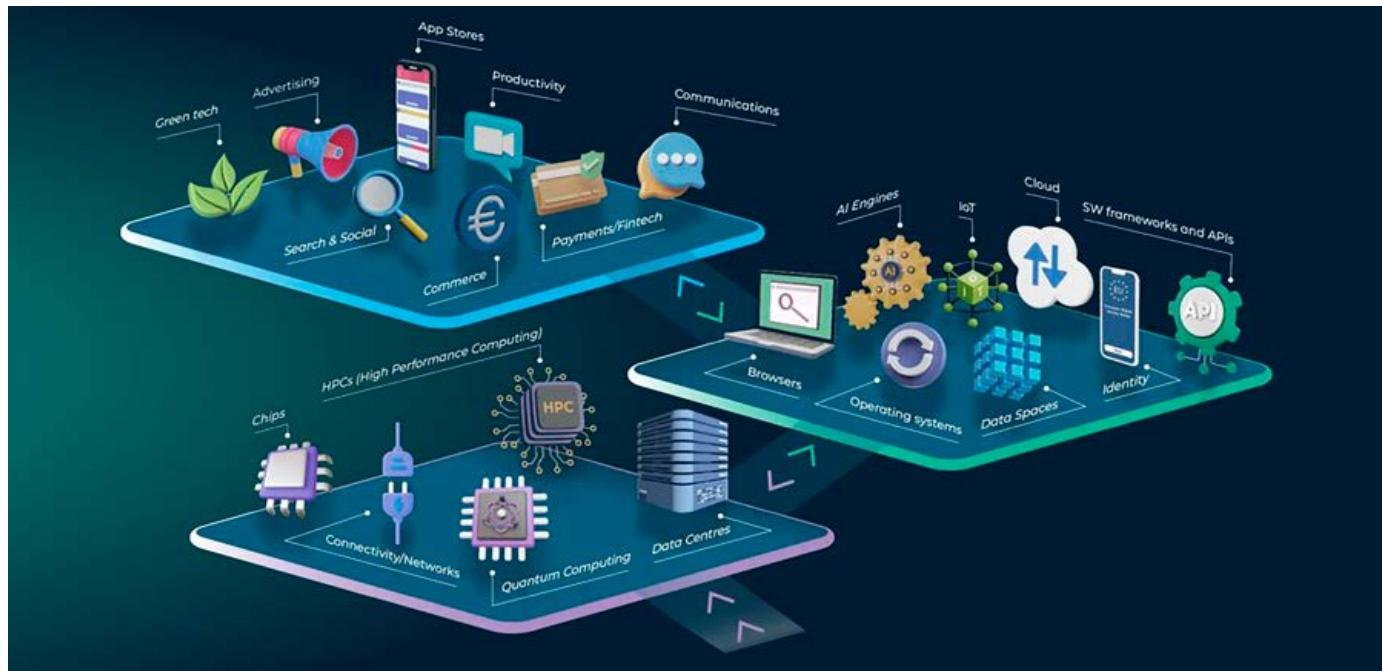

### Sovereign European Provider: The EuroStack framework

EuroStack, which has evolved from a broad, informal coalition into a non-profit association, aims to provide a pragmatic response to this situation. To avoid vague definitions and what Stéfane refers to as 'sovereignty washing', where 'non-European providers use marketing and superficial corporate structures to create an illusion of compliance', EuroStack has translated the concept of 'digital sovereignty' into a concrete, legally robust framework built on five pillars, as set out below:

- 1. Jurisdiction and governance – accountability to EU law:** the ultimate parent entity of the provider must be headquartered and legally incorporated in the European Territory (EU, EEA, EFTA), and must be free from decisive non-EU control.

- 2. Technical sovereignty – freedom from technological lock-in:** an antidote to the scenario in which Europeans' data is in Europe but trapped within proprietary foreign technology. 'We mandate that services be built predominantly on open-source software and implement open standards, guaranteeing data portability, interoperability, and even operational reversibility,' explains Stéfane.

- 3. Operational sovereignty – control over the entire service-delivery chain:** 'It's not enough for data to reside in the EU; it must also be managed from the EU. We require that the entire physical infrastructure – and, critically, the operational control plane – are located and operated from within Europe,' says Stéfane. 'All personnel with privileged access must be European residents, employed by a European entity, and working from within the EU.'

EuroStack graphic showing the digital ecosystem

## Special feature: Digital sovereignty

4. **Data sovereignty – verifiable protection of all data:** exclusive EU residency for all data, including metadata and backups, with additional credits for verifiable technical measures that make it impossible for any unauthorized party – including the provider itself – to access unencrypted data.

5. **Economic sovereignty – a net contributor to the European economy:** ‘This ensures that public money is used to build our own industrial base. We require that the majority of a provider’s research and development (R+D) expenditure and personnel for the core technology are located in Europe, and that their business model is fair and transparent, free from punitive tactics like exorbitant data egress fees,’ Stéfane says.

### From ideas to action: EuroStack’s priorities for digital sovereignty

With all this in mind, how should European actors – in both the public and private sectors – move forward to reverse the trend towards digital subjection?

EuroStack has defined three priorities for action, as follows:

#### 1. ‘Buy European’: Drive demand through strategic procurement

‘We must amend EU public-procurement directives to mandate that a significant and growing share of public IT spending is directed towards sovereign European solutions,’ says Stéfane. ‘This isn’t protectionism; it’s a strategic investment in our own industrial base. It creates the vital customer revenue that our companies need to scale and compete.’ Cristina agrees unequivocally: ‘Every other region in the world says, “buy from yourself”. The default in Europe is “buy from everywhere”. It might have made sense originally because we don’t want individual states in Europe to just buy from themselves – but now it is being weaponized against us by the hyperscalers,’ she says. ‘The outflow of public procurement to the US is around €80 billion a year, so if we reserved 20–30% to European suppliers via strategic public procurement rules, the “shot in the arm” would be sizeable.’